## Memory Module Specifications

### KVR24R17S4/8

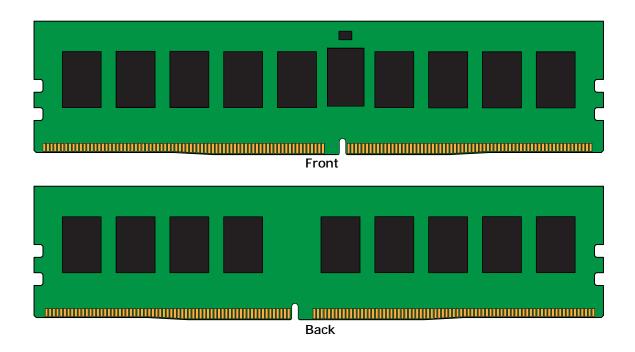

8GB 1Rx4 1G x 72-Bit PC4-2400 CL17 Registered w/Parity 288-Pin DIMM

#### DESCRIPTION

ValueRAM's KVR24R17S4/8 is a 1G x 72-bit (8GB) DDR4-2400 CL17 SDRAM (Synchronous DRAM) registered w/ parity, 1Rx4, ECC, memory module, based on eighteen 1G x 4-bit FBGA components. The SPD is programmed to JEDEC standard latency DDR4-2400 timing of 17-17-17 at 1.2V. Each 288-pin DIMM uses gold contact fingers. The electrical and mechanical specifications are as follows:

# SPECIFICATIONS CLUDD)

| CL(IDD)                                                  | 15 cycles         |

|----------------------------------------------------------|-------------------|

| Row Cycle Time (tRCmin)                                  | 46.16ns(min.)     |

| Refresh to Active/Refresh Command Time 1x mode (tRFCmin) | 260ns(min.)       |

| Row Active Time (tRASmin)                                | 32.00ns(min.)     |

| Maximum Operating Power                                  | TBD W*            |

| UL Rating                                                | 94 V - 0          |

| Operating Temperature                                    | 0° C to +85° C    |

| Storage Temperature                                      | -55° C to +100° C |

<sup>\*</sup>Power will vary depending on the SDRAM used.

### **FEATURES**

- Power Supply: VDD=1.2V (1.14V to 1.26V)

- VDDQ = 1.2V (1.14V to 1.26V)

- VPP 2.5V (2.375V to 2.75V)

- VDDSPD=2.25V to 2.75V

- · Functionality and operations comply with the DDR4 SDRAM datasheet

- 16 internal banks

- Bank Grouping is applied, and CAS to CAS latency (tCCD\_L, tCCD\_S) for the banks in the same or different bank group accesses are available

- Data transfer rates: PC4-2400. PC4-2133, PC4-1866, PC4-1600

- · Bi-Directional Differential Data Strobe

- 8 bit pre-fetch

- Burst Length (BL) switch on-the-fly BL8 or BC4(Burst Chop)

- Supports ECC error correction and detection

- On-Die Termination (ODT)

- Temperature sensor with integrated SPD

- This product is in compliance with the RoHS directive.

- · Per DRAM Addressability is supported

- · Internal Vref DQ level generation is available

- Write CRC is supported at all speed grades

- · CA parity (Command/Address Parity) mode is supported

Continued >>

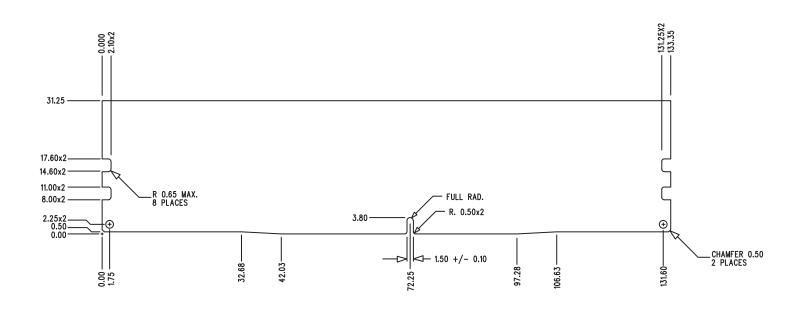

### **MODULE DIMENSIONS**