获得世界领先主板制造商的认证{{Footnote.N64682}}

经过测试和认证,因此您可以信心满满地使用喜欢的主板进行组装和升级。

DDR5 是第 5 代双倍数据速率同步动态随机存取内存,又称 DDR5 SDRAM。DDR5 是在 2017 年由行业标准机构 JEDEC(联合电子器件工程委员会)开始推动的,并采纳了来自金士顿等全球领先内存半导体和芯片组架构供应商的意见,设计了一些全新特性,可以提高性能、降低功耗并增强数据完整性,为未来十年的计算提供支持。DDR5 问世于 2021 年。

DDR5 的起始速度为 4800MT/s{{Footnote.A65242}},而 DDR4 的最高速度为 3200MT/s。这表示带宽增长 50%。DDR5 与计算平台版本保持同步,计划将标准速度提升至 8800MT/s,甚至更高。

采用 1.1V 的 DDR5 的功耗比采用 1.2V 的 DDR4 对等组件下降 20% 左右。这不仅可以延长笔记本电脑的电池续航时间,还可以为日夜不停运行的企业服务器带来重大优势。

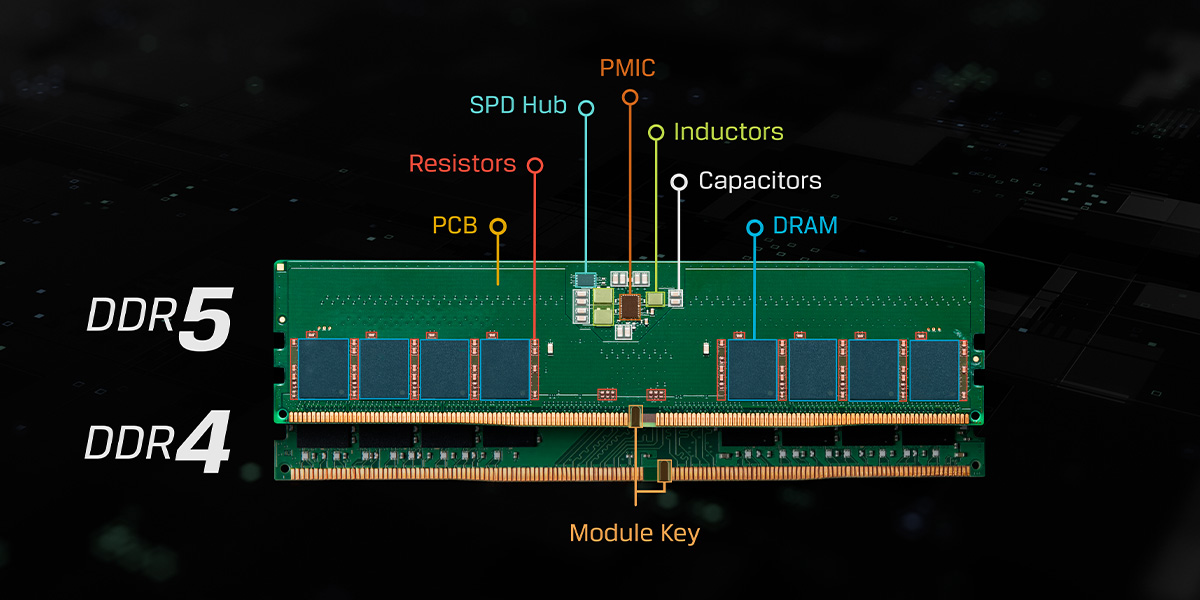

DDR5 模块采用板载电源管理集成电路 (PMIC),帮助调节内存模组中不同组件(DRAM、寄存器、SPD hub 等)所需的电源。对于服务器级模组,PMIC 采用 12V;对于 PC 级模组,PMIC 采用 5V。相比前几代内存,这可以实现更好的功率分布、提高信号完整性并减少噪音。

DDR5 采用将串行存在检测 (SPD) EEPROM 与更多 hub 功能相集成的新装置,从而管理对外部控制器的访问并将内部总线上的内存负载与外部分离开。

DDR5 将内存模组分成两个独立的 32 位可寻址子通道,以提高内存控制器数据访问的效率并减少延迟。DDR5 模组的数据带宽仍是 64 位,但将其分成两个 32 位可寻址通道可提高总体性能。对于服务器级内存 (RDIMM),向每个子通道添加了 8 位用于 ECC 支持,最终达到每个子通道 40 位或每列 80 位。双列模组包含四个 32 位子通道。

此模组中央的槽口作用就像钥匙,与 DDR5 插槽匹配,避免安装 DDR4、DDR3 或其他不受支持的模组类型。与 DDR4 不同,DDR5 模块键为以下模组类型采用不同的键:UDIMM 和 RDIMM

片内 ECC(纠错代码)是一项用于纠正 DRAM 芯片内位错误的新功能。随着晶圆光刻技术不断改进,DRAM 芯片密度不断提高,导致数据泄露的可能性加大。片内 ECC 通过纠正芯片内的错误来规避这种风险,从而提高可靠性并降低缺陷率。对于在此芯片外发生的错误或在模组与 CPU 内的内存控制器之间的总线上发生的错误,这项技术则无法纠正。用于服务器和工作站的支持 ECC 的处理器具备可以动态纠正单位错误或多位错误的编码。必须提供额外的 DRAM 位来允许此纠正操作发生,这适用于 ECC 级模组类型,例如 ECC 无缓冲模组、带寄存器的模组和 降载模组。

服务器级 DDR5 RDIMM 向模组末端添加了温度传感器,用于监测整个 DIMM 长度上的热状况。这样可以更精细地控制系统散热,而不会像 DDR4 一样因高温造成性能瓶颈。

DDR5 将列数从 16 个增加到 32 个,从而可以同时打开更多页面,提高了效率。此外还将最小突发长度增加一倍至 16,DDR4 为 8。这可以提高数据总线效率并进而在总线上提供两倍的数据量,最终减少存取相同缓存数据线的读取/写入操作数量。

DDR5 添加了一个名为 SAME-BANK Refresh 的新命令,允许仅刷新每个列组中的一个列,而不是所有列。相比 DDR4,DDR5 可利用此命令进一步改善性能和效率。

DDR5 利用 Decision Feedback Equalization (DFE) 在模组上提供稳定、可靠的信号完整性,满足高带宽的要求。

尽管此内存模组看起来像 DDR4,但存在一些重大改变,使得它们无法兼容旧系统。键位置(中央的槽口)做了调整,避免被安装到不兼容的插槽。

经过测试和认证,因此您可以信心满满地使用喜欢的主板进行组装和升级。

| 数据速率(单位 MT/s){{Footnote.A65242}} | 3600、4000、4400、4800、5200、5600、6000、6400、6800、7200、7600、8000、8400、8800 |

| 单块 DRAM 密度 (Gbit) | 8Gb、16Gb、24Gb、32Gb、48Gb、64Gb |

| 封装类型和 Ballout(x4、x8 / x16) | BGA、3DS TSV(78、82 / 102) |

| 传输接口 | |

|---|---|

| 电压 (VDD / VDDQ / VPP) | 1.1 / 1.1 / 1.8 V |

| 内部 VREF | VREFDQ、VREFCA、VREFCS |

| 命令/地址 | POD (Pseudo Open Drain) |

| 均衡 | DFE (Dynamic Feedback Equalization) |

| 突发长度 | BL16 / BC8 / BL32(可选) |

| 核心架构 | |

| 列数 | 32 列(8 个列组) 8 BG x 4 列 (16-64Gb x4/x8) 8 BG x 2 列 (8Gb x4/x8) 16 列(4 个列组) 4 BG x 4 列 (16-64Gb x16) 4 BG x 2 列 (8Gb x16) |

| 页面大小 (x4 / x8 / x16) | 1KB / 1KB / 2KB |

| 预取 | 16n |

| DCA(工作周期调整) | DQS 和 DQ |

| 内部 DQS 延迟监测 | DQS 内部振荡器 |

| ODECC(片内 ECC) | 128b+8b SEC 错误检查和清理 |

| CRC(循环冗余检验) | 读取/写入 |

| ODT(片内终结) | DQ、DQS、DM、CA 总线 |

| MIR(“Mirror”引脚) | 是 |

| 总线反转 | 命令/地址反转 (CAI) |

| CA 调驯、CS 调驯 | CA 调驯、CS 调驯 |

| 写入均衡调驯模式 | 改进 |

| 读取调驯模式 | 针对用户定义的串行、时钟和 LFSR 生成的训练模式的专用 MR |

| 模式寄存器 | 多达 256 x 8 位 |

| PRECHARGE 命令 | 所有列、按列和相同列 |

| REFRESH 命令 | 所有列和相同列 |

| Loopback 模式 | 是 |