Fehlerentdeckung und -korrektur

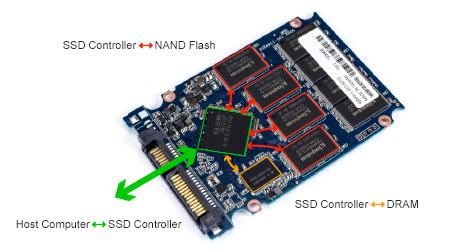

SSDs müssen dafür sorgen, dass die Integrität der Daten während der Übertragung vom Host-PC auf den NAND-Speicher erhalten bleibt. Dies erfolgt über den SSD-Controller. Daten, die vom Host auf die SSD übertragen werden, bevor sie letztendlich auf den NAND-Flashspeicher geschrieben werden, bezeichnet man auch oft als „Daten in Transit“. SSD-Controller haben eine eingebaute Technik zur Fehlerkorrektur (ECC für Error Correction Code genannt), mit der die große Mehrheit von Fehlern erkannt und korrigiert wird, die Daten in ihrer Übertragungsbahn behindern können. Flashspeicher-Chips enthalten zusätzliche Daten zur Fehlerkorrektur und zu jedem Block, in den Daten geschrieben wurden. Diese Informationen ermöglichen dem SSD-Controller beim Lesen eines Datenblocks gleichzeitig viele Fehler zu korrigieren. NAND-Flashspeicher stoßen im Normalbetrieb, genau wie Festplatten, auf Bit-Fehler, die sie mit ihren ECC-Daten während des Transfers korrigieren.

In seltenen Fällen können Datenfehler in einem Block, der gelesen wird, nicht korrigiert werden. Der SSD-Controller erkennt diese Einschränkung als Uncorrectable ECC Error (UECC - nicht korrigierbaren Fehler) und meldet dem Host-Computer den Fehler. SSDs sind für extreme Zuverlässigkeit konzipiert. UECCs kommen in Client SSDs im Normalfall in einem Verhältnis von eins zu 10

je 15 gelesene Bits vor; und bei Enterprise SSDs im Verhältnis von eins zu 10 je 16 gelesene Bits. Unter Ansatz der JEDEC JEDS218A und JESD219 UBER-Vorgaben für SSDs der Enterprise-Klasse wird bei einem Vergleich zwischen Enterprise-SSDs und Client-SSDs erwartet, dass bei einem Verhältnis von 1 Bitfehler je 10 Billiarden Bits (~1.11 Petabytes) nur 1 nicht behebbarer Bitfehler auftritt, im Gegensatz von Client-SSDs mit 1 Bitfehler je gelesene 1 Billiarde Bits.

Im NAND-Flash von Kingston SSDs sind zudem freie Blöcke integriert. Diese Speicherbereiche liegen normalerweise im Over-Provisioned (OP) Bereich eines Laufwerks und sind für den Benutzer nicht zugänglich. Wenn ein NAND in einem Datenblock eine übermäßig hohe Anzahl Fehler hat, wird dieser Block als „fehlerhafter Block“ gekennzeichnet , entfernt und durch einen freien Block ersetzt. Die Daten werden im Laufe dieses Verfahrens erforderlichenfalls mit ECC korrigiert. Die Verwendung von freien Blöcken verlängert die Nutzungsdauer und Langlebigkeit von SSD-Laufwerken.