Pregunte a un experto

Para planificar la solución adecuada es necesario conocer los requisitos de su sistema y de sus proyectos. Permita que los expertos de Kingston le orienten.

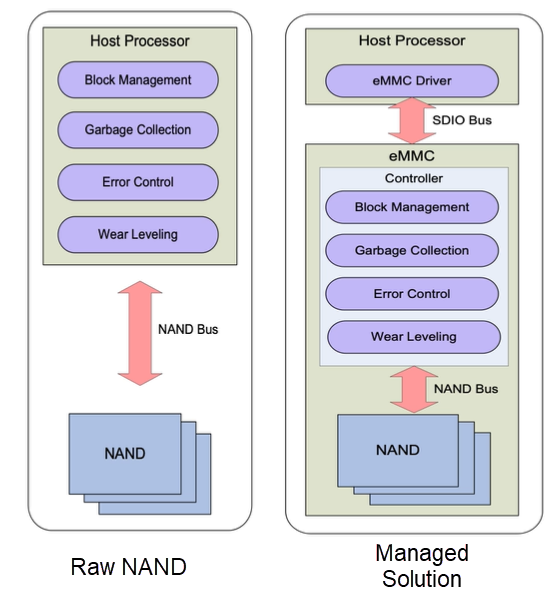

El almacenamiento NAND Flash no es un simple medio de datos para lectura/escritura. Para un uso confiable, se deben implementar varios algoritmos: Manejo de bloques NAND, recolección de basura, control de errores y nivelación de desgaste. La NAND Flash moderna se maneja con algoritmos en el dispositivo de almacenamiento, no implementados en el procesador host. Esto beneficia a sus usuarios, ya que hace que el manejo de la NAND sea menos complejo para el host y simplifica el soporte y el mantenimiento del producto.

Las escrituras del host en NAND Flash tienen ineficiencias que pueden hacer que el medio falle antes. La unidad organizativa más pequeña de NAND es la página, que se puede leer y programar pero no borrar. La única unidad organizativa que se puede borrar es el bloque, que consta de muchas páginas. Por lo tanto, las páginas no se pueden sobrescribir hasta que se borre un bloque. Los bloques pueden fallar con el tiempo a medida que se alcanza su nivel de resistencia. También pueden ocurrir defectos que conduzcan a fallas tempranas.

NAND Flash tiene ciclos limitados disponibles de borrado de programas. Alcanzar ese límite significa que el dispositivo está en estado EoL (finalizando su vida útil), lo que significa que ya no es confiable. La resistencia varía según la configuración de las celdas NAND.

Configuración de celda de un solo nivel: esta configuración tiene la mayor resistencia y el mayor margen de error.

|

eMMC LBA 512B Sector Address |

NAND Page & Block Address |

| 0:31 | Blk10, Pg101 |

| 32:63 | Blk10, Pg102 |

| 64:95 | Blk10, Pg103 |

| 96:127 | Blk10, Pg104 |

| 128:159 | Blk15, Pg57 |

| 160:191 | Blk8, Pg129 |

| 192:223 | Blk10, Pg107 |

| 224:255 | Blk22, Pg88 |

eMMC lee y escribe en unidades de sector de 512 bytes, que son lógicas, no físicas. Las direcciones de sector se denominan direcciones de bloques lógicos o LBAs. Cuando se modifican los datos, no es práctico borrar todo el bloque NAND, lo que provoca un desgaste ineficiente en las páginas que no cambiaron. Un esquema de mapeo LBA-PBA (dirección de bloque físico) proporciona escrituras más pequeñas para equilibrar el desgaste del bloque, una práctica llamada nivelación de desgaste. Por medio de una tabla de traducción de direcciones, los LBA se asignan a los PBA. Este proceso equilibra el desgaste del bloque y mejora la velocidad de escritura.

El proceso de mapeo de direcciones funciona de la siguiente manera:

Las reescrituras pequeñas, aleatorias y no alineadas con la página suelen ser la mayor fuente de Amplificación de escritura. Para minimizar WAF, las escrituras deben alinearse en un límite de página en múltiplos de unidades de tamaño de página. Este tamaño de unidad óptimo se encuentra en el campo Tamaño de escritura óptimo del registro CSD extendido.

La fórmula para determinar el total de Bytes escritos, o TBW, es sencilla:

A menudo, WAF está entre 4 y 8, pero depende del comportamiento de escritura del sistema host. Por ejemplo, las escrituras secuenciales grandes producen un WAF más bajo, mientras que las escrituras aleatorias de pequeños bloques de datos producen un WAF más alto. A menudo, este tipo de comportamiento puede provocar fallas prematuras en los dispositivos de almacenamiento.

Por ejemplo, un eMMC de 4GB con un factor de resistencia de 3000 y un WAF de 8 equivaldrá a:

El total de Bytes escritos del dispositivo eMMC es de 1.5 TB. Por lo tanto, podemos escribir 1.5 TB de datos durante el ciclo de vida del producto antes de alcanzar su estado EoL.

Para estimar sus requisitos de TBW, calcule el uso diario del dispositivo en cuestión. Por ejemplo, una carga de trabajo con 500 MB de uso diario de escritura (y un ciclo de vida previsto de 5 años) necesitará un dispositivo que pueda alcanzar un TBW superior a 915 GB:

El TBW se puede utilizar para determinar el WAF máximo permitido para un dispositivo, ya que TBW = (DC * EF) / WAF. Si la vida útil de su dispositivo no puede alcanzar el TBW objetivo para la aplicación de su producto, puede intentar mejorarlo. Considere ponerlo en el modo Pseudo Single Level Cell, que puede aumentar diez veces la resistencia al convertir el dispositivo de TLC o MLC al modo de un solo bit por celda (single-bit-per-cell). Sin embargo, esto reduce drásticamente la capacidad: 50% para un dispositivo MLC de dos bits por celda y más del 66% para un dispositivo TLC de tres bits. Si esta solución no le satisface, elegir un dispositivo más grande para manejar la misma carga de trabajo también ayuda. Un dispositivo con el doble de capacidad tendrá el doble de TBW.

Los algoritmos eMMC de Kingston logran un bajo factor de amplificación de escritura. Ofrecemos múltiples configuraciones para equilibrar el rendimiento, la vida útil y la confiabilidad. La antigüedad del dispositivo se puede monitorear utilizando las herramientas de estimación de vida útil de JEDEC archivadas en EXT_CSD, una función compartida con todos los dispositivos eMMC. La vida útil se informa en incrementos del 10 % en función de la resistencia del dispositivo. Una herramienta informa la antigüedad de los bloques NAND Flash configurados con TLC o MLC, mientras que la otra informa la antigüedad de los bloques configurados en modo pseudo-SLC. Los dispositivos eMMC de Kingston también tienen comandos de proveedores para devolver la antigüedad promedio de los bloques del dispositivo. Estas son más precisas que las herramientas JEDEC pero requieren un poco de desarrollo de software para su uso. Alternativamente, puede enviar su dispositivo antiguo a Kingston para un análisis más completo.

#KingstonIsWithYou

Para planificar la solución adecuada es necesario conocer los requisitos de su sistema y de sus proyectos. Permita que los expertos de Kingston le orienten.

La longevidad del producto es una preocupación clave para muchas aplicaciones integradas que normalmente requieren una vida útil de 7-10 años. Dado el rápido ritmo al que la tecnología avanza y cambia, el mantenimiento a largo plazo de los productos integrados puede ser un desafío.

Es importante comprender cómo se gestiona la memoria flash NAND en eMMC en los dispositivos modernos y cómo se relaciona con su ciclo de vida. Esta guía ayudará a los diseñadores e ingenieros a comprender cómo estimar y validar la vida útil de un dispositivo de almacenamiento eMMC para el diseño de su sistema.