Demandez à un expert

Planifier la bonne solution requiert la compréhension des exigences de votre projet et de votre système. Les experts de Kingston Technology sont là pour vous aider.

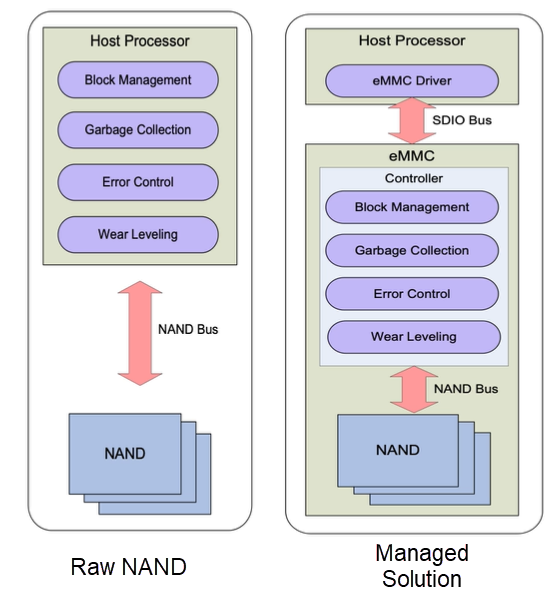

Le stockage flash NAND n’est pas un simple support de données en lecture/écriture. Pour une utilisation fiable, plusieurs algorithmes doivent être mis en œuvre : gestion des blocs NAND, garbage collection, contrôle des erreurs et répartition de l’usure. La mémoire flash NAND moderne est gérée à l’aide d’algorithmes présents sur l’appareil de stockage, et non pas implémentée dans le processeur hôte. C’est un avantage pour ses utilisateurs, car cela rend la gestion NAND moins complexe pour l’hôte et simplifie l’assistance et la maintenance du produit.

Les écritures de l’hôte dans la mémoire flash NAND présentent des inefficacités qui peuvent entraîner une défaillance précoce du support. La plus petite unité organisationnelle de NAND est la page, qui peut être lue et programmée mais pas effacée. La seule unité organisationnelle qui peut être effacée est le bloc, lequel se compose de plusieurs pages. Par conséquent, les pages ne peuvent pas être écrasées tant qu’un bloc n’est pas effacé. Au fil du temps, les blocs peuvent tomber en panne lorsque leur niveau d’endurance est atteint. Des défauts entraînant des défaillances précoces peuvent également se produire.

La mémoire flash NAND dispose d’un nombre limité de cycles de programmation et d’effacement. Atteindre cette limite signifie que le appareil est en état EoL (« End of Life », fin de vie), c’est-à-dire qu’il n’est plus fiable. L’endurance varie en fonction de la configuration des cellules NAND.

Configuration de cellule à un seul niveau : cette configuration présente l’endurance la plus élevée et la plus grande marge d’erreur.

|

eMMC LBA 512B Sector Address |

NAND Page & Block Address |

| 0:31 | Blk10, Pg101 |

| 32:63 | Blk10, Pg102 |

| 64:95 | Blk10, Pg103 |

| 96:127 | Blk10, Pg104 |

| 128:159 | Blk15, Pg57 |

| 160:191 | Blk8, Pg129 |

| 192:223 | Blk10, Pg107 |

| 224:255 | Blk22, Pg88 |

L’eMMC lit et écrit dans des unités de secteur de 512 octets, lesquelles sont logiques et non pas physiques. Les adresses de secteur sont appelées adresses de bloc logique (« Logical Block Addresses », LBA). Lorsque les données sont modifiées, l’effacement de l’ensemble du bloc NAND est peu pratique, ce qui entraîne une usure inutile des pages qui n’ont pas changé. Un schéma de mappage LBA-PBA (« Physical Block Address », adresse de bloc physique) permet des écritures plus petites pour équilibrer l’usure du bloc. Cette pratique est appelée répartition de l’usure. Au moyen d’une table de traduction d’adresses, les LBA sont mappées en PBA. Ce processus équilibre l’usure des blocs et améliore la vitesse d’écriture.

Le processus de mappage d’adresse fonctionne comme suit :

Les petites réécritures aléatoires et non alignées sur une page sont généralement la plus grande source d’amplification d’écriture. Pour minimiser le WAF, les écritures doivent être alignées sur une limite de page en multiples d’unités de taille de page. Cette taille d’unité optimale se trouve dans le champ Optimal Write Size du registre Extended CSD.

La formule permettant de déterminer le nombre total d’octets écrits (« Total Bytes Written », TBW) est simple :

Souvent, le WAF se situe entre 4 et 8, mais il dépend du comportement d’écriture du système hôte. Par exemple, les grandes écritures séquentielles produisent un WAF plus faible, tandis que les écritures aléatoires de petits blocs de données produisent un WAF plus élevé. Ce type de comportement peut souvent entraîner une défaillance précoce des appareils de stockage.

Par exemple, une eMMC de 4 Go avec un facteur d’endurance de 3 000 et un WAF de 8 équivaudra à :

Le total des octets écrits de l’appareil eMMC est de 1,5 To. Par conséquent, nous pouvons écrire 1,5 To de données pendant le cycle de vie du produit avant d’atteindre son état EoL.

Pour évaluer vos besoins en TBW, estimez l’utilisation quotidienne de l’appareil en question. Par exemple, une charge de travail présentant une utilisation d’écriture de 500 Mo par jour (et un cycle de vie prévu de 5 ans) nécessitera un appareil pouvant atteindre un TBW supérieur à 915 Go :

Le TBW peut être utilisé pour déterminer le WAF maximal autorisé pour un appareil, puisque TBW = (DC * EF) / WAF. Si la durée de vie de votre appareil ne peut pas atteindre le TBW cible pour l’application de votre produit, vous pouvez essayer de l’améliorer. Envisagez de le mettre en mode Pseudo Single Level Cell (pseudo cellule à niveau unique), qui peut décupler l’endurance en convertissant l’appareil de TLC ou MLC en mode à un seul bit par cellule. Cependant, cela réduit considérablement la capacité : 50 % pour un appareil MLC à deux bits par cellule, et plus de 66 % pour un appareil TLC à trois bits. Si cette solution n’est pas satisfaisante pour vous, vous pouvez opter pour un appareil plus grand pour traiter la même charge de travail. Un appareil ayant deux fois plus de capacité aura deux fois plus de TBW.

Les algorithmes eMMC de Kingston atteignent un faible facteur d’amplification en écriture. Nous proposons plusieurs configurations pour équilibrer les performances, la durée de vie et la fiabilité. L’âge de l’appareil peut être contrôlé à l’aide des outils d’estimation de la durée de vie du JEDEC présents dans l’EXT_CSD, une fonctionnalité partagée avec tous les appareils eMMC. La durée de vie est indiquée par incréments de 10 % en fonction de l’endurance de l’appareil. Un outil rapporte l’âge des blocs flash NAND configurés en TLC ou MLC, tandis que l’autre rapporte l’âge des blocs configurés en mode pseudo-SLC. Les appareils eMMC de Kingston disposent également de commandes fournisseur pour renvoyer l’âge moyen des blocs du appareil. Ces commandes sont plus précises que les outils du JEDEC, mais leur utilisation nécessite un peu de développement logiciel. Vous pouvez également envoyer votre appareil âgé à Kingston pour une analyse plus complète.

#KingstonIsWithYou

Planifier la bonne solution requiert la compréhension des exigences de votre projet et de votre système. Les experts de Kingston Technology sont là pour vous aider.

La longévité des produits est une préoccupation majeure pour de nombreuses applications embarquées qui nécessitent généralement une durée de vie de 7 à 10 ans. Compte tenu du rythme rapide auquel la technologie progresse et évolue, le maintien à long terme des produits embarqués peut être difficile.

Il est important de comprendre comment la flash NAND de l’eMMC est gérée dans les appareils modernes et comment cela se rapporte à son cycle de vie. Ce guide aidera les concepteurs et les ingénieurs à comprendre comment estimer et valider la durée de vie utile d’un périphérique de stockage eMMC dans la conception de leur système.