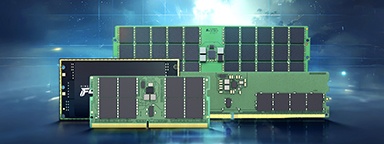

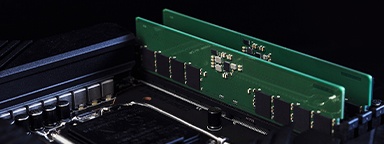

随着 DDR5 标准速度在下一代台式机和笔记本电脑中越来越快,稳定性和数据完整性成为亟待解决的关键问题。速度的提升意味着电子噪声和抖动成为棘手问题,可能导致错误、数据丢失或系统冻结。为应对这一挑战,负责维护内存行业标准的 JEDEC 组织在 2023 年底为 DDR5 无缓冲双列直插式内存模块(DDR5 Unbuffered DIMM)和小型双列直插式内存模块(DDR5 SODIMM)提出了新的要求。从 6400MT/s DDR5 的推出开始,必须在内存模块中添加客户时钟驱动器(CKD)组件,以重新驱动时钟信号,从而减少噪声和抖动,并全面提高信号完整性。

时钟信号通常由处理器生成,是电压和电流信号,以恒定频率在高电平和低电平之间振荡。这些信号使主板上的组件能够同步,从而确保数据能够及时发送和接收。有了模块上的时钟驱动器,它将生成自己的时钟信号,以确保模块上的精确时序同步。