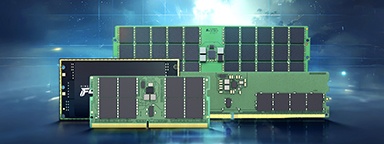

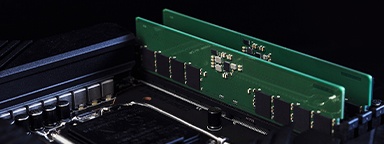

A medida que las velocidades estándar de DDR5 se vuelven cada vez más rápidas para las computadoras de escritorio y portátiles de última generación, la estabilidad y la integridad de los datos se convierten en problemas críticos que deben mitigarse. Al aumentar la velocidad, el ruido electrónico y las fluctuaciones se convierten en un problema que puede provocar errores, pérdida de datos o bloqueos del sistema. Para hacer frente a este reto, el organismo encargado de mantener los estándares de la industria en materia de memoria, JEDEC, especificó un nuevo requisito a finales de 2023 para los módulos DIMM DDR5 sin búfer (Dual Inline Memory Module o Módulo de memoria dual en línea) y los módulos SODIMM DDR5 (Small Outline Dual Inline Memory Module o Módulo de memoria dual en línea de contorno pequeño). A partir de la introducción de DDR5 de 6400Mt/s, es necesario añadir el componente Controlador de reloj de cliente o Client Clock Driver (CKD) al módulo de memoria para redirigir la señal de reloj, minimizando el ruido, las fluctuaciones y el ruido general.

Las señales de reloj, tradicionalmente generadas por el procesador, son señales de voltaje y corriente que fluyen a una frecuencia constante, oscilando entre estados altos y bajos. Estas señales permiten que los componentes se sincronicen a través de la placa madre, así los datos se envían y llegan a tiempo. Con el controlador de reloj en el módulo, éste generará su propia señal de reloj para garantizar una sincronización precisa en el módulo.