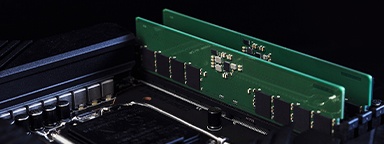

A medida que crecen las velocidades estándar de DDR5 para los ordenadores portátiles y de sobremesa de última generación, la integridad de los datos y la estabilidad se erigen como temas cruciales que se han de controlar. Los aumentos de la velocidad hacen que las vibraciones y el ruido de los aparatos electrónicos se conviertan en un problema que podría provocar errores, pérdidas de datos o interrupciones del sistema. Con el objetivo de abordar este reto, a finales de 2023, el organismo encargado de salvaguardar los estándares del sector en materia de memoria, el JEDEC, especificó una nueva normativa para los módulos DIMM (o módulo de memoria en línea doble) sin búfer DDR5 y los SODIMM (o DIMM de formato pequeño) DDR5. A raíz de la introducción de los DDR5 de 6400MT/s, se debe agregar al módulo de memoria un componente de controlador de reloj de cliente (CKD) que reconduzca la señal de reloj, lo que minimizaría el ruido y las vibraciones y mejoraría la integridad de la señal en general.

Las señales de reloj, que tradicionalmente las generaba el procesador, son señales de corriente y voltaje que fluyen a una frecuencia constante, oscilando entre estados altos y bajos. Estas señales permiten que los componentes se sincronicen a través de la placa base, de forma que los datos se envíen y lleguen a tiempo. Gracias al controlador de reloj presente en el módulo, este generará su propia señal de reloj para garantizar una sincronización temporal precisa.