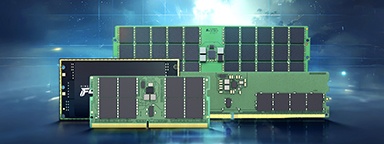

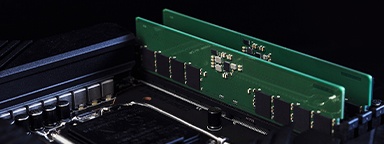

Wraz ze wzrostem szybkości standardu DDR5 w komputerach stacjonarnych i laptopach nowej generacji coraz ważniejsza staje się kwestia stabilności i integralności danych. Wzrost szybkości powoduje problemy związane z zakłóceniami i szumem elektronicznym, które mogą skutkować błędami, utratą danych lub zawieszeniem się systemu. Aby je rozwiązać, JEDEC – organizacja definiująca standardy w branży pamięci – określiła pod koniec 2023 r. nowe wymagania dla modułów DDR5 Unbuffered DIMM (Dual Inline Memory Module) i DDR5 SODIMM (Small Outline Dual Inline Memory Module). Począwszy od wprowadzenia standardu pamięci DDR5 o szybkości 6400MT/s moduły muszą być dodatkowo wyposażone w komponent Client Clock Driver (CKD), który przesterowuje sygnał zegara, minimalizując szumy i zakłócenia oraz ogólnie poprawiając integralność sygnału.

Sygnały zegara, tradycyjnie generowane przez procesor, to sygnały napięciowe i prądowe, które przepływają ze stałą częstotliwością, oscylując między stanami wysokim i niskim. Sygnały te umożliwiają synchronizację działania komponentów na płycie głównej, aby przesyłane dane docierały do nich w odpowiednim czasie. Sterownik zegara w module generuje własny sygnał zegara, aby zapewnić precyzyjną synchronizację taktowania w module.