Von den weltweit führenden Motherboard-Herstellern geprüft{{Footnote.N64682}}

Getestet und genehmigt, damit du dein bevorzugtes Motherboard mit Zuversicht einsetzen und aufrüsten kannst.

DDR5 ist die 5. Generation des synchronen dynamischen Direktzugriffsspeichers mit doppelter Datenrate, auch bekannt als DDR5 SDRAM. Die Entwicklung begann 2017 von der Industriestandardisierungsorganisation JEDEC (Joint Electron Device Engineering Council) unter Mitwirkung der weltweit führenden Hersteller von Speicherhalbleitern und Chipsatzarchitekturen, darunter Kingston. DDR5 bietet neue Funktionen für höhere Leistung, geringeren Stromverbrauch und robustere Datenintegrität für das nächste Jahrzehnt der Computertechnik. DDR5 wird 2021 eingeführt.

DDR5 beginnt bei 4800MT/s{{Footnote.A65242}}, während DDR4 eine Höchstgeschwindigkeit von 3200MT/s erreicht. Dies entspricht einer Steigerung der Bandbreite um 50 %. Im Einklang mit den Veröffentlichungen von Computerplattformen sind für DDR5 Standardgeschwindigkeiten geplant, die bis zu 8800MT/s und möglicherweise darüber hinaus reichen.

Bei 1,1 V verbraucht DDR5 ca. 20 % weniger Strom als entsprechende DDR4-Komponenten bei 1,2 V. Dies schont nicht nur die Akkulaufzeit von Laptops, sondern hat auch einen erheblichen Vorteil für Unternehmensserver, die rund um die Uhr arbeiten.

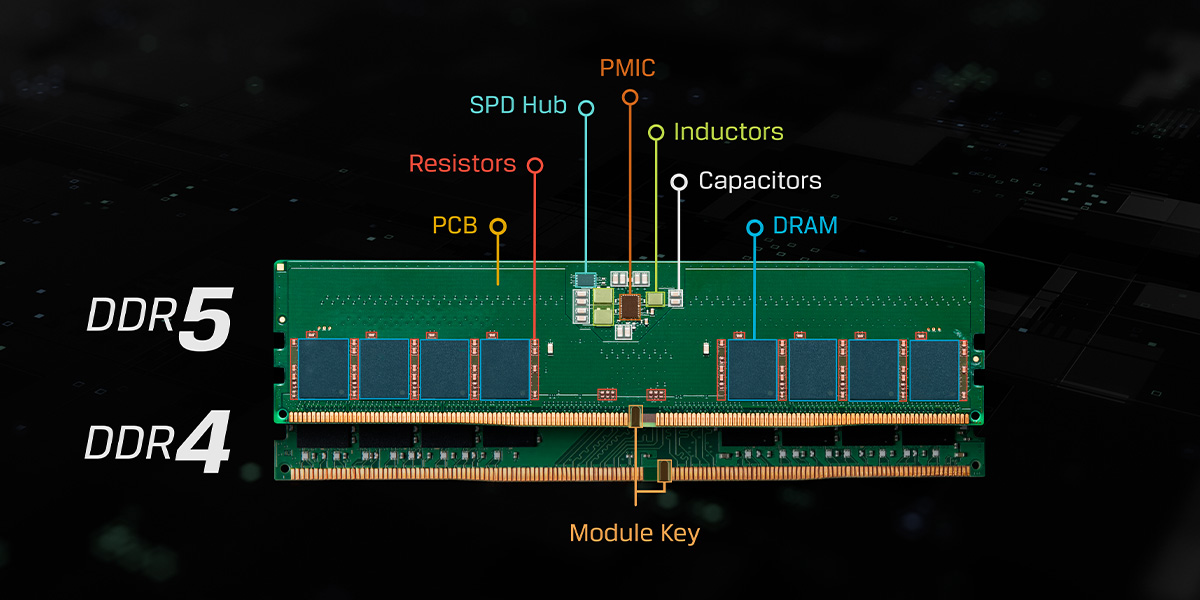

DDR5-Module verfügen über integrierte Power Management Integrate Circuits (PMIC), die dazu beitragen, den Strombedarf der verschiedenen Komponenten des Speichermoduls (DRAM, Register, SPD Hub usw.) zu regulieren. Bei Modulen der Serverklasse verwendet der PMIC 12 V, bei Modulen der PC-Klasse 5 V. Dies sorgt für eine bessere Energieverteilung als bei früheren Generationen, verbessert die Signalintegrität und reduziert das Rauschen.

DDR5 verwendet einen neuen Baustein, der das Serial Presence Detect (SPD) EEPROM mit zusätzlichen Hub-Funktionen integriert, den Zugriff auf den externen Controller verwaltet und die Speicherlast auf dem internen Bus von der externen entkoppelt.

DDR5 teilt das Speichermodul in zwei unabhängige, adressierbare 32-Bit-Suchannels auf, um die Effizienz zu erhöhen und die Latenzzeiten der Datenzugriffe für den Speicher-Controller zu verringern. Die Datenbreite des DDR5-Moduls beträgt nach wie vor 64 Bit, die Aufteilung in zwei adressierbare 32-Bit-Kanäle erhöht jedoch die Gesamtleistung. Für Speicher der Serverklasse (RDIMMs) werden jedem Subchannel 8 Bits für ECC-Unterstützung hinzugefügt, was insgesamt 40 Bits pro Subchannel oder 80 Bits pro Rang ergibt. Dual Rank-Module verfügen über vier 32-bit subchannels.

Die Kerbe in der Mitte des Moduls wirkt wie ein Schlüssel, der auf DDR5-Sockel ausgerichtet ist, um zu verhindern, dass DDR4-, DDR3- oder andere nicht unterstützte Modultypen installiert werden. Im Gegensatz zu DDR4 unterscheiden sich die DDR5-Modulschlüssel zwischen den Modultypen: UDIMM und RDIMM

On-Die ECC (Error Correction Code) ist eine neue Funktion zur Korrektur von Bitfehlern innerhalb des DRAM-Chips. Da die Dichte der DRAM-Chips durch die schrumpfende Wafer-Lithografie zunimmt, steigt auch das Potenzial für Datenverluste. On-Die ECC mindert dieses Risiko, indem es Fehler innerhalb des Chips korrigiert, die Zuverlässigkeit erhöht und die Fehlerquote verringert. Diese Technologie kann keine Fehler korrigieren, die außerhalb des Chips oder auf dem Bus zwischen dem Modul und dem in der CPU untergebrachten Speicher-Controller auftreten. ECC-fähige Prozessoren für Server und Workstations verfügen über eine Kodierung, die Einzel- oder Multibit-Fehler im laufenden Betrieb korrigieren kann. Um diese Korrektur zu ermöglichen, müssen zusätzliche DRAM-Bits zur Verfügung stehen, die bei Modultypen der ECC-Klasse wie ECC unbuffered, Registered und Load Reduced.

DDR5 RDIMMs der Serverklasse verfügen über Temperatursensoren an den Enden der Module, um die thermischen Bedingungen über die gesamte Länge des DIMMs zu überwachen. Dies ermöglicht eine präzisere Steuerung der Systemkühlung, im Gegensatz zur Drosselung der Leistung, wie bei DDR4 bei hohen Temperaturen.

DDR5 verdoppelt die Anzahl der Bänke von 16 auf 32. Dadurch können mehr Seiten gleichzeitig geöffnet werden, was die Effizienz erhöht. Ebenfalls verdoppelt wurde die minimale Burst-Länge, die bei DDR4 von 8 auf 16 erhöht wurde. Dies verbessert die Effizienz des Datenbusses, da die doppelte Datenmenge auf dem Bus zur Verfügung steht, und reduziert folglich die Anzahl der Lese-/Schreibvorgänge für den Zugriff auf dieselbe Cache-Datenzeile.

DDR5 fügt einen neuen Befehl namens SAME-BANK Refresh hinzu, der die Refreshes von nur einer Bank pro Bankgruppe und nicht von allen Bänken ermöglicht. Im Vergleich zu DDR4 ermöglicht dieser Befehl DDR5 eine weitere Verbesserung von Leistung und Effizienz.

DDR5 verwendet Decision Feedback Equalization (DFE), um eine stabile, zuverlässige Signalintegrität auf dem Modul zu gewährleisten, die für eine hohe Bandbreite erforderlich ist.

Die Speichermodule selbst sehen zwar ähnlich aus wie die DDR4-Module, aber es gibt erhebliche Änderungen, die sie mit älteren Systemen inkompatibel machen. Die Position des Schlüssels (Kerbe in der Mitte) wird verschoben, um zu verhindern, dass er in inkompatible Steckdosen eingebaut wird.

Getestet und genehmigt, damit du dein bevorzugtes Motherboard mit Zuversicht einsetzen und aufrüsten kannst.

| Datenraten (Geschwindigkeit in MT/s){{Footnote.A65242}} | 3600, 4000, 4400, 4800, 5200, 5600, 6000, 6400, 6800, 7200, 7600, 8000, 8400, 8800 |

| Monolithische DRAM-Dichten (Gbit) | 8Gb, 16Gb, 24Gb, 32Gb, 48Gb, 64Gb |

| Gehäusetyp und Ballout (x4, x8 / x16) | BGA, 3DS TSV (78, 82 / 102) |

| Schnittstelle | |

|---|---|

| Spannung (VDD / VDDQ / VPP) | 1.1 / 1.1 / 1.8 V |

| Intern VREF | VREFDQ, VREFCA, VREFCS |

| Befehl/Adresse | POD (Pseudo Open Drain) |

| Equalization | DFE (Dynamic Feedback Equalization) |

| Burst-Länge | BL16 / BC8 / BL32 (optional) |

| Core -Architektur | |

| Anzahl der Bänke | 32 Bänke (8 Bankgruppen) 8 BG x 4 Bänke (16-64Gb x4/x8) 8 BG x 2 Bänke (8Gb x4/x8) 16 Bänke (4 Bankgruppen) 4 BG x 4 Bänke (16-64Gb x16) 4 BG x 2 Bänke (8Gb x16) |

| Seitengröße (x4 / x8 / x16) | 1KB / 1KB / 2KB |

| Prefetch | 16n |

| DCA (Duty Cycle Adjustment) | DQS und DQ |

| Internal DQS Delay Monitoring | DQS Interval Oscillator |

| ODECC (On-die ECC) | 128b+8b SEC-Fehlerprüfung und Scrub |

| CRC (Cyclic Redundancy Check) | Lesen/Schreiben |

| ODT (On-die Termination) | DQ, DQS, DM, CA bus |

| MIR („Mirror“-Pin) | Ja |

| Bus Inversion | Command/Address Inversion (CAI) |

| CA Training, CS Training | CA training, CS training |

| Write Leveling Training Modes | Verbessert |

| Read Training Patterns | Dedizierte MRs für benutzerdefinierte serielle, taktgesteuerte und LFSR -generierte Trainingsmuster |

| Modus-Register | Bis zu 256 x 8 Bits |

| PRECHARGE-Befehle | Alle Bänke, pro Bank und dieselbe Bank |

| REFRESH-Befehle | Alle Bänke und dieselbe Bank |

| Loopback-Modus | Ja |