Được chứng nhận bởi các nhà sản xuất bo mạch chủ hàng đầu thế giới{{Footnote.N64682}}

Đã được thử nghiệm và chứng nhận để bạn tự tin xây dựng và nâng cấp trên bo mạch chủ yêu thích của mình.

DDR5 là Bộ nhớ truy cập ngẫu nhiên động đồng bộ Tốc độ dữ liệu gấp đôi thế hệ thứ 5, hay còn gọi là SDRAM DDR5. Câu chuyện của DDR5 bắt đầu từ năm 2017 với sự khởi xướng của JEDEC (Hội đồng Kỹ thuật Thiết bị Điện tử) – một tổ chức về các tiêu chuẩn ngành, cùng với những đóng góp từ các nhà sản xuất bán dẫn bộ nhớ và kiến trúc chipset hàng đầu trên toàn cầu, trong đó có cả Kingston. DDR5 được thiết kế với các tính năng mới để hứa hẹn mang đến hiệu năng cao hơn, mức điện năng thấp hơn và tính toàn vẹn dữ liệu mạnh mẽ hơn cho công nghệ điện toán trong thập kỉ tới. DDR5 ra mắt vào năm 2021.

DDR5 có tốc độ tối thiểu là 4800 MT/giây{{Footnote.A65242}}, trong khi DDR4 chỉ đạt tối đa 3200 MT/giây. Điều này tương đương với mức tăng 50% về băng thông. Cùng với sự ra mắt của các nền tảng tính toán, DDR5 dự kiến tăng tốc độ tiêu chuẩn tăng lên 8800 MT/giây, có thể là hơn thế nữa.

Ở mức 1,1V, DDR5 tiêu thụ ít hơn khoảng 20% điện năng so với các cấu phần DDR4 tương đương hoạt động ở mức 1,2V. Bên cạnh việc bảo tồn thời lượng pin cho máy tính xách tay, DDR5 còn mang lại lợi thế rất lớn cho các máy chủ doanh nghiệp có tần suất hoạt động mạnh.

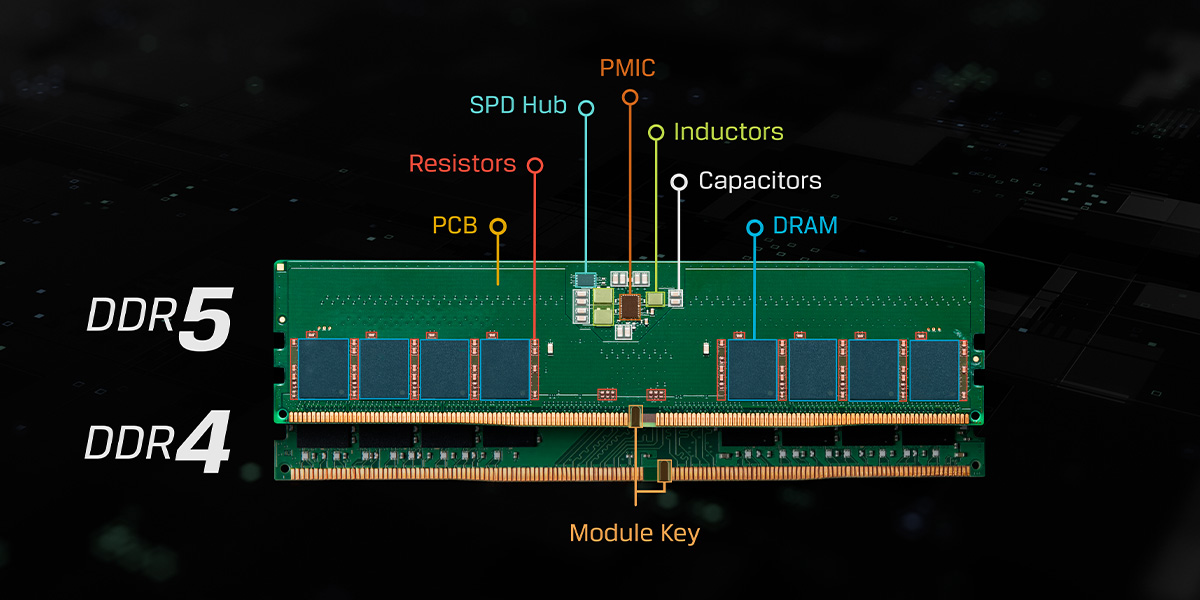

Mô-đun DDR5 được trang bị Mạch tích hợp quản lý nguồn điện (PMIC), giúp điều phối mức điện năng mà các cấu phần khác nhau của mô-đun bộ nhớ cần đến (như DRAM, Thanh ghi, hub SPD, v.v.). Với các mô-đun cấp máy chủ, PMIC sử dụng 12V, còn với các mô-đun cấp PC, PMIC sử dụng mức 5V. Công nghệ này có khả năng hỗ trợ điều phối điện năng tốt hơn so với các thế hệ trước, từ đó giúp giảm nhiễu và mang lại tín hiệu toàn vẹn hơn.

DDR5 sử dụng một thiết bị mới để tích hợp EEPROM Phát hiện hiện diện nối tiếp (SPD) với các tính năng hub bổ sung, quản lý quyền truy cập vào các trình điều khiển bên ngoài và ngắt kết nối các tải bộ nhớ trên bus trong khỏi bên ngoài.

DDR5 phân chia mô-đun bộ nhớ thành hai kênh phụ khả định 32 bit độc lập để nhằm tăng hiệu suất và giảm độ trễ khi truy cập dữ liệu cho trình điều khiển bộ nhớ. Độ rộng dữ liệu của mô-đun DDR5 vẫn là 64 bit, nhưng việc chia nhỏ thành hai kênh khả định 32 bit sẽ giúp tăng hiệu năng tổng thể. Đối với bộ nhớ cấp máy chủ (RDIMM), chúng tôi bổ sung thêm 8 bit cho mỗi kênh phụ này để hỗ trợ ECC, đạt tổng 40 bit mỗi kênh phụ, hay tổng 80 bit mỗi Bậc. Mô-đun Bậc đôi được trang bị bốn kênh phụ 32 bit.

Phần rãnh nằm ở giữa mô-đun đóng vai trò như khóa, giúp khớp bộ nhớ vào khe cắm dành cho DDR5, tránh việc người dùng lắp đặt nhầm DDR4, DDR3 hay các loại mô-đun không được hỗ trợ khác. Không giống như DDR4, rãnh khóa của DDR5 có sự khác biệt giữa các loại mô-đun: UDIMM và RDIMM

ECC (Mã sửa lỗi) trên chip bán dẫn là một tính năng mới được thiết kế để sửa các lỗi bit trong chip DRAM. Khi tăng mật độ chip của DRAM bằng công nghệ quang khắc trên phiến silicon mỏng thu hẹp, nguy cơ rò rỉ dữ liệu cũng tăng lên. ECC trên chip bán dẫn giúp giảm thiểu rủi ro này bằng cách sửa các lỗi xảy ra trong chip, từ đó tăng độ tin cậy và giảm tỷ lệ sai sót. Công nghệ này không thể sửa các lỗi nằm ngoài chip hoặc lỗi xảy ra trên bus giữa mô-đun và trình điều khiển bộ nhớ nằm trong CPU. Bộ xử lý dựa trên ECC dành cho máy chủ và các trạm làm việc được trang bị các mã có khả năng sửa lỗi bit đơn hoặc nhiều bit khi đang chạy. Các bit DRAM bổ sung cũng phải được cung cấp để cho phép triển khai quy trình sửa lỗi này. Tính năng này có mặt trên các loại mô-đun cấp ECC như ECC Không có bộ đệm, Có thanh ghi và Giảm tải.

Các RDIMM DDR5 cấp máy chủ được lắp thêm cảm biến nhiệt ở các đầu của thanh RAM để theo dõi điều kiện nhiệt độ trên khắp thân DIMM. Việc này giúp quá trình kiểm soát việc làm mát hệ thống được chính xác hơn, tránh tình trạng giảm hiệu năng ở nhiệt độ cao như DDR4.

DDR5 có băng nhớ tăng gấp đôi từ 16 lên 32, cho phép người dùng mở nhiều trang cùng một lúc và tăng hiệu suất. Ngoài ra, chiều dài truyền loạt tối thiểu cũng tăng lên đến 16, so với 8 ở thế hệ DDR4. Những cải tiến này giúp tăng cường hiệu suất bus dữ liệu, cung cấp gấp đôi dữ liệu trên bus, từ đó giảm mức đọc/ghi cần thiết để truy cập cùng một dòng dữ liệu bộ đệm.

DDR5 được bổ sung một lệnh mới gọi là SAME-BANK Refresh (Làm mới CÙNG BĂNG NHỚ), để cho phép làm mới chỉ một băng nhớ mỗi nhóm băng nhớ, thay vì làm mới tất cả các băng nhớ. So với DDR4, lệnh này giúp DDR5 cải tiến hiệu năng và hiệu suất cao hơn nữa.

DDR5 sử dụng công nghệ Cân bằng phản hồi quyết định (DFE) để mang đến tính toàn vẹn ổn định và đáng tin cậy cho tín hiệu trên mô-đun, cũng là yêu cầu cần thiết đối với mức băng thông cao.

Mặc dù thanh RAM trông khá giống với DDR4, thế hệ mới này có một số thay đổi đáng kể khiến chúng không còn tương thích với các hệ thống cũ. Vị trí rãnh khóa (phần rãnh nằm ở giữa) được di chuyển để tránh người dùng lắp nhầm vào khe cắm không tương thích.

Đã được thử nghiệm và chứng nhận để bạn tự tin xây dựng và nâng cấp trên bo mạch chủ yêu thích của mình.

| Tốc độ dữ liệu (Tốc độ tính bằng MT/s){{Footnote.A65242}} | 3600, 4000, 4400, 4800, 5200, 5600, 6000, 6400, 6800, 7200, 7600, 8000, 8400, 8800 |

| Mật độ DRAM một khối (Gbit) | 8Gb, 16Gb, 24Gb, 32Gb, 48Gb, 64Gb |

| Loại đóng gói và bi đỡ (x4, x8 / x16) | BGA, 3DS TSV (78, 82 / 102) |

| Giao diện | |

|---|---|

| Điện áp (VDD / VDDQ / VPP) | 1,1 / 1,1 / 1,8 V |

| VREF trong | VREFDQ, VREFCA, VREFCS |

| Lệnh/Địa chỉ | POD (Trình điều khiển Pseudo Open Drain) |

| Cân bằng | DFE (Cân bằng phản hồi động) |

| Chiều dài truyền loạt | BL16 / BC8 / BL32 (tùy chọn) |

| Kiến trúc lõi | |

| Số băng nhớ | 32 Băng nhớ (8 Nhóm băng nhớ) 8 Nhóm băng nhớ x 4 băng nhớ (16-64Gb x4/x8) 8 Nhóm băng nhớ x 2 băng nhớ (8Gb x4/x8) 16 Băng nhớ (4 Nhóm băng nhớ) 4 Nhóm băng nhớ x 4 băng nhớ (16-64Gb x16) 4 Nhóm băng nhớ x 2 băng nhớ (8Gb x16) |

| Kích cỡ trang (x4 / x8 / x16) | 1KB / 1KB / 2KB |

| Tìm nạp trước | 16n |

| DCA (Điều chỉnh chu kỳ hoạt động) | DQS và DQ |

| Giám sát độ trễ DQS trong | Bộ tạo dao động ngắt quãng DQS |

| ODECC (ECC trên chip bán dẫn) | SEC kiểm tra và sửa lỗi 128b+8b |

| CRC (Kiểm tra dự phòng theo chu kỳ) | Đọc/Ghi |

| ODT (Điện trở đầu cuối đặt trong chip bán dẫn) | Bus DQ, DQS, DM, CA |

| MIR (chân "Mirror") | Có |

| Đảo bus | Đảo lệnh/địa chỉ (CAI) |

| Đào tạo CA, Đào tạo CS | Đào tạo CA, đào tạo CS |

| Chế độ đào tạo cân bằng ghi | Được cải tiến |

| Mô hình đào tạo đọc | MR chuyên dụng dành cho các mô hình đào tạo nối tiếp do người dùng quy định, dạng đồng hồ và do LFSR tạo. |

| Thanh ghi chế độ | Lên đến 256 x 8 bit |

| Lệnh PRECHARGE (NẠP TRƯỚC) | Tất cả băng nhớ, mỗi băng nhớ và cùng một băng nhớ |

| Lệnh REFRESH (LÀM MỚI) | Tất cả băng nhớ và cùng một băng nhớ |

| Chế độ Loopback | Có |