世界大手マザーボードメーカーから認定取得{{Footnote.N64682}}

テストおよび承認済みですので、好きなマザーボード上に安心して構築およびアップグレードできます。

DDR5 は、ダブルデータレートシンクロナスダイナミックランダムアクセスメモリの第 5 世代(DDR5 SDRAM)です。DDR5 の開発は 2017 年から、業界標準化団体の合同電子デバイス委員会 (JEDEC) によって、Kingston など世界的な大手半導体およびチップセットアーキテクチャのベンダからの意見を反映して進められており、今後 10 年のコンピューティングに対応するため、パフォーマンス向上、省電力、データ完全性の強化などの新機能を備えています。 DDR5 は 2021 年に登場しました。

DDR5 は 4800MT/s{{Footnote.A65242}} から始まりますが、DDR4 の最高速度は 3200MT/s です。これは、帯域幅が 50% 向上したことを意味します。コンピュートプラットフォームのリリースに合わせ、DDR5 では 8800MT/秒まで、場合によってはそれ以上の標準速度が計画されています。

1.1V の場合 DDR5 では、同等の DDR4 コンポーネントで 1.2V の場合よりも消費電力が最大 20% 削減されます。ノートパソコンでバッテリ寿命を延長する一方で、24 時間稼働のエンタプライズサーバーにも大きなメリットがあります。

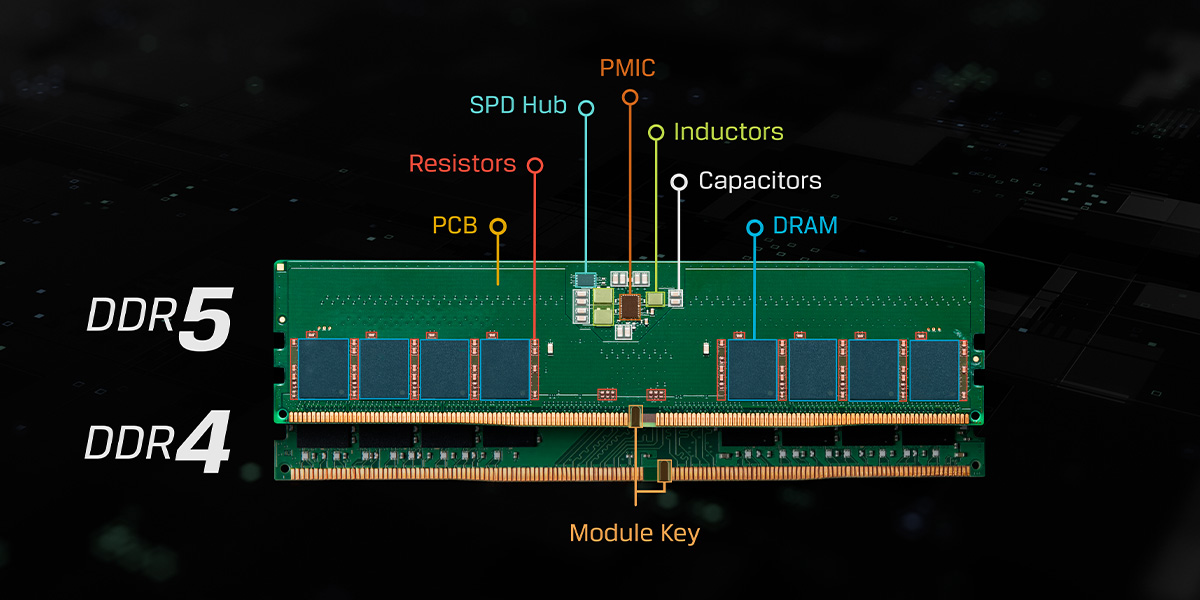

DDR5 モジュールには、オンボード電源管理用集積回路(PMIC)が搭載され、メモリモジュール(DRAM、レジスタ、SPD ハブなど)の各種コンポーネントに必要な電力の調整を支援します。サーバークラスモジュールの場合、PMIC は 12V を使用し、PC クラスモジュールの場合、PMIC は 5V を使用します。これにより、前世代より電力分配が改善され、信号品位が向上し、雑音が少なくなります。

DDR5 では、SPD(シリアル存在検出) EEPROM を追加ハブ機構と統合した新しいデバイスを活用して、外部コントローラへのアクセスを管理し、内部バスのメモリの負荷を外部から分離します。

DDR5 では、メモリコントローラによるデータアクセスの効率向上とレイテンシ低下のため、メモリモジュールを 2 つの独立した 32 ビットのアドレッシング可能なサブチャネルに分割しています。DDR5 モジュールのデータ幅は依然として 64 ビットですが、2 つの 32 ビットのアドレッシング可能なサブチャネルに分割したことで、全体のパフォーマンスを向上させます。 サーバークラスメモリ(RDIMM)の場合、ECC のサポートのために各サブチャネルに 8 ビット追加され、サブチャネルあたり合計 40 ビット、ランクあたり 80 ビットとなっています。デュアルランクモジュール機構には 4 つの 32 ビットサブチャネルが搭載されています。

モジュール中央には、DDR5 ソケットの位置に合わせた切り込みがあり、キーのような働きをして、DDR4 や DDR3 などのサポート対象外のモジュールタイプの挿入を防止します。DDR4 と異なり、DDR5 モジュールのキーは、UDIMM および RDIMM のモジュールタイプとは異なる位置にあります。

オンダイ ECC(エラー修正コード)は、DRAM チップ中のビットエラーを修正するために設計された新機能です。ウェーハリソグラフィーの微細化によって DRAM チップの密度が増加しているため、データ流出の可能性が増加しています。オンダイ ECCでは、チップ内のエラーを修正してこのリスクを軽減することによって、信頼性を向上し欠陥率を低減しています。ただし、この技術では、チップの外のエラーや、CPU の中にあるモジュールとメモリコントローラの間のバスで発生したエラーを修正できません。 ECC に対応するサーバーやワークステーションのプロセッサは、シングルビットまたはマルチビットのエラーを実行中に修正できるコーディングを備えています。この修正を可能にするには、ECC Unbuffered(ECC アンバッファード)、Registered(レジスタード)、Load Reduced (負荷低減)などの ECC クラスモジュールタイプに搭載された追加 DRAM ビットが 利用可能でなければなりません。

サーバークラスの DDR5 RDIMM には、モジュールの端に温度センサーが追加されており、DIMM の長さ全体にわたって放熱状態を監視します。これにより、DDR4 で見られた高温時の性能低下とは対照的に、システム冷却をより正確に制御できるようになりました。

DDR5 ではバンクが 16 から 32 に増加しています。これにより、同時にオープンできるページ数が増加し、効率が向上します。また、最小バースト長も、DDR4 の 8 から 16 に倍増します。これにより、データバス効率が向上し、バスに 2 倍のデータを提供しますので、同じキャッシュデータ行にアクセスする読み取り/書き込みの回数が減少します。

DDR5 では、SAME-BANK Refresh という新しいコマンドが追加されており、バンクグループごとにバンクすべてではなく、1 つのバンクだけをリフレッシュできます。DDR4 と比較して、このコマンドによって DDR5 のパフォーマンスと効率をさらに向上することが可能です。

DDR5 では DFE(判定帰還型等化器)を活用して、高帯域に必要な安定した信頼性の高い信号品位をモジュール上で提供します。

メモリモジュール自体は DDR4 と似ているように見えるが、レガシーシステムとの互換性を失わせる大きな変更があります。互換性のないソケットに取り付けられないように、キーの位置 (中央の切り欠き) が移動しています。

テストおよび承認済みですので、好きなマザーボード上に安心して構築およびアップグレードできます。

| データ転送速度(MT/s 単位){{Footnote.A65242}} | 3600、4000、4400、4800、5200、5600、6000、6400、6800、7200、 7600、8000、8400、8800 |

| モノリシック DRAM 密度(Gbit) | 8Gb、16Gb、24Gb、32Gb、48Gb、64Gb |

| パッケージタイプおよびボールアウト(x4、x8 / x16) | BGA、3DS TSV(78、82 / 102) |

| インタフェース | |

|---|---|

| 電圧(VDD / VDDQ / VPP) | 1.1 / 1.1 / 1.8 V |

| 内部 VREF | VREFDQ、VREFCA、VREFCS |

| コマンド/アドレス | POD(疑似オープンドレイン) |

| 等化 | DFE(判定帰還型等化器) |

| バースト長 | BL16 / BC8 / BL32(オプション) |

| コアアーキテクチャ | |

| バンク数 | 32 バンク(8 バンクグループ) 8 BG x 4 バンク(16~64Gb x4/x8) 8 BG x 2 バンク(8Gb x4/x8) 16 バンク(4 バンクグループ) 4 BG x 4 バンク(16~64Gb x16) 4 BG x 2 バンク(8Gb x16) |

| ページサイズ(x4 / x8 / x16) | 1KB / 1KB / 2KB |

| プリフェッチ | 16n |

| DCA(デューティサイクル調整) | DQS および DQ |

| 内部 DQS 遅延モニタリング | DQS インターバルオシレータ |

| オンダイ ECC(ODECC) | 128b+8b SEC エラーチェックおよびスクラブ |

| 巡回冗長検査(CRC) | 読み取り/書き込み速度 |

| オンダイ終端(ODT) | DQ、DQS、DM、CA バス |

| MIR(「ミラー」ピン) | あり |

| バス反転 | コマンド/アドレス反転(CAI) |

| CA トレーニング、CS トレーニング | CA トレーニング、CS トレーニング |

| 書き込み平準化トレーニングモード | 改善後 |

| 読み取りトレーニングパターン | ユーザー定義シリアル専用 MR、クロック、および LFSR -生成トレーニングパターン |

| Mode registers | Up to 256 x 8 bits |

| PRECHARGE コマンド | 全バンク、バンクごと、同一バンク |

| REFRESH コマンド | 全バンクおよび同一バンク |

| ループバックモード | あり |