Сертифицировано ведущими производителями системных плат{{Footnote.N64682}}

Модули протестированы и одобрены, поэтому вы можете с уверенностью создавать свою конфигурацию и модернизировать систему на предпочитаемой системной плате.

DDR5 — это 5-е поколение синхронной динамической оперативной памяти с удвоенной скоростью передачи данных (Double Data Rate Synchronous Dynamic Random Access Memory), также называемая DDR5 SDRAM. Разработка была начата в 2017 году огранизацией по отраслевым стандартам JEDEC (Объединенный инженерный совет по электронным устройствам) при участии ведущих мировых поставщиков полупроводниковой памяти и архитектур наборов микросхем, включая Kingston. Память DDR5 обладает новыми функциями для повышения производительности, снижения энергопотребления и более высокой целостности данных для вычислительных систем следующего десятилетия. Память DDR5 была представлена в 2021 г.

Скорость памяти DDR5 начинается с 4800 МТ/с{{Footnote.A65242}}, в то время как в случае DDR4 она достигает 3200 МТ/с. Это означает, что пропускная способность увеличивается на 50%. Развиваясь в соответствии с выпусками вычислительных платформ, планируется, что стандартная скорость памяти DDR5 будет достигать 8800 МТ/с или даже больше.

Работая при напряжении 1,1 В, модуль памяти DDR5 потребляет примерно на 20% меньше энергии по сравнению с аналогичными модулями DDR4, работающими при напряжении 1,2 В. Увеличивая время автономной работы ноутбуков, это также обеспечивает значительное преимущество для корпоративных серверов, работающих круглосуточно.

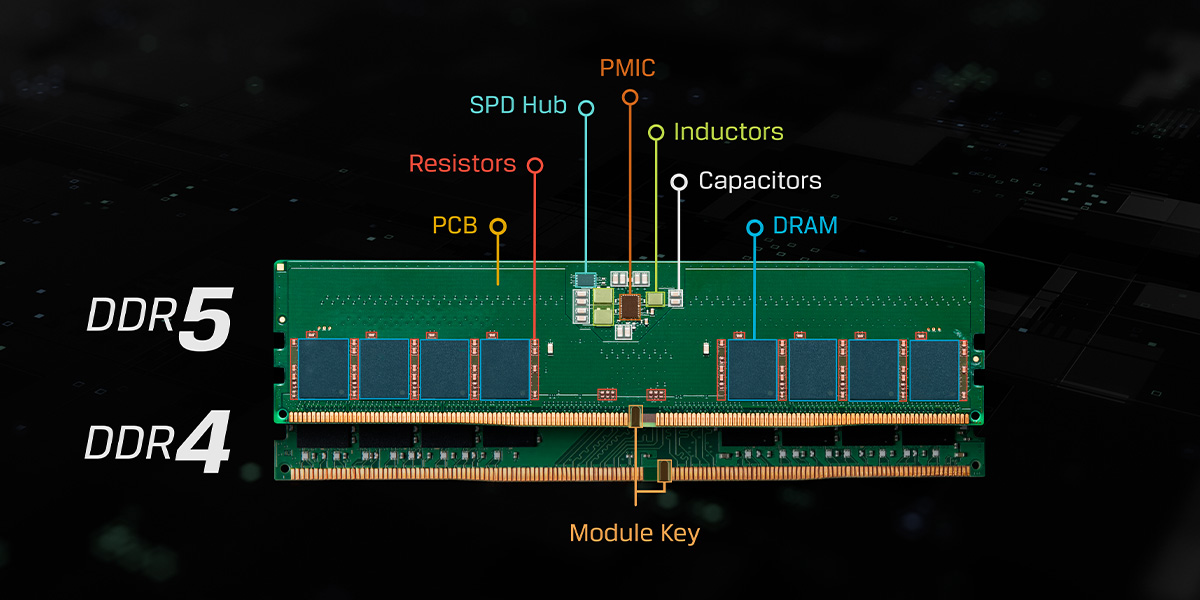

Модули DDR5 оснащаются встроенными микросхемами управления питанием (PMIC), которые помогают регулировать мощность, необходимую для различных компонентов модуля памяти (DRAM, регистр, концентратор SPD и т. д.). В модулях серверного класса PMIC использует 12 В, а в модулей класса ПК — 5 В. Это обеспечивает лучшее распределение мощности по сравнению с предыдущими поколениями, повышает целостность сигнала и снижает уровень шума.

В DDR5 используется новое устройство, объединяющее энергонезависимую память (EEPROM) функции последовательной идентификации модуля памяти (SPD) с дополнительными функциями концентратора, управляющее доступом к внешнему контроллеру и отделяющее нагрузку на внутреннюю шину памяти от внешней.

DDR5 разделяет модуль памяти на два независимых 32-битных адресуемых подканала, что позволяет повысить эффективность и снизить время ожидания доступа к данным для контроллера памяти. Разрядность данных модуля DDR5 по-прежнему составляет 64 бита, однако разделение на два 32-битных адресуемых канала увеличивает общую производительность. Для памяти серверного класса (RDIMM) к каждому подканалу добавляется 8 бит для поддержки функции ECC. В результате получаем 40 бит на подканал или 80 бит на ранг памяти. Двухранговые модули имеют четыре 32-битных подканала.

Вырез в центре модуля действует как ключ, соответствующий разъемам DDR5, чтобы предотвратить установку модулей DDR4, DDR3 или других неподдерживаемых типов модулей. В отличие от DDR4, ключи модуля DDR5 различаются для разных типов модулей: UDIMM и RDIMM

On-Die ECC (Error Correction Code) — новая функция, предназначенная для исправления битовых ошибок в микросхеме DRAM. По мере увеличения плотности чипов DRAM за счет уменьшения литографии на пластинах возрастает вероятность утечки данных. On-Die ECC функция обнаружения и исправления ошибок снижает этот риск, исправляя ошибки в микросхеме, повышая надежность и снижая количество дефектов. Эта технология не может исправлять ошибки за пределами микросхемы или ошибки, которые возникают в шине между модулем и контроллером памяти, находящимся в ЦП. Процессоры с поддержкой ECC для серверов и рабочих станций имеют кодировку, которая может исправлять одно- или многобитные ошибки на лету. Для выполнения такого исправления должны быть доступны дополнительные биты DRAM, которые присутствуют в модулях памяти класса ECC, таких как небуферизованные модули с ECC, регистровые модули и модули со сниженной нагрузкой.

На концах модулей RDIMM DDR5 серверного класса добавлены датчики температуры для контроля теплового режима по всей длине модуля DIMM. Это позволяет более точно контролировать охлаждение системы, в отличие от дросселирования тактов для защиты от перегрева, используемой в DDR4 при высоких температурах.

В DDR5 удвоено количества блоков памяти (с 16 до 32). Это позволяет открывать больше страниц одновременно, повышая эффективность. Также вдвое увеличена минимальная длина серийной очереди: до 16 по сравнению с 8 для DDR4. Это повышает эффективность работы шины данных, позволяя передавать по ней вдвое больше данных, и, следовательно, уменьшает количество операций чтения/записи, необходимых для доступа к одной и той же строке данных кэша.

В DDR5 добавлена новая команда, SAME-BANK Refresh, которая позволяет обновлять только один банк памяти в каждой группе банков, а не все банки. По сравнению с DDR4 эта команда позволяет еще больше повысить производительность и эффективность памяти DDR5.

В модулях памяти DDR5 использует эквализацию обратной связи по принятию решений (DFE) для обеспечения стабильной и надежной целостности сигнала в модуле, которая необходима для высокой пропускной способности.

Хотя эти модули памяти похожи на DDR4, в них внесены существенные изменения, в результате которых они несовместимыми с прежними системами. Расположение ключа (выемка в центре) перемещена, чтобы предотвратить установку модуля в несовместимые разъемы.

Модули протестированы и одобрены, поэтому вы можете с уверенностью создавать свою конфигурацию и модернизировать систему на предпочитаемой системной плате.

| Скорость передачи данных (скорость в MT/s){{Footnote.A65242}} | 3600, 4000, 4400, 4800, 5200, 5600, 6000, 6400, 6800, 7200, 7600, 8000, 8400, 8800 |

| Плотность интегральной микросхемы DRAM (Гбит) | 8 Гбит, 16 Гбит, 24 Гбит, 32 Гбит, 48 Гбит, 64 Гбит |

| Тип и формат пакетов (x4, x8 / x16) | BGA, 3DS TSV (78, 82 / 102) |

| Интерфейс | |

|---|---|

| Напряжение (VDD / VDDQ / VPP) | 1,1 / 1,1 / 1,8 В |

| Внутреннее напряжение VREF | VREFDQ, VREFCA, VREFCS |

| Команда/адрес | POD (Pseudo Open Drain) |

| Компенсация | DFE (Dynamic Feedback Equalization) |

| Длина пакета импульсов | BL16 / BC8 / BL32 (опция) |

| Базовая архитектура | |

| Количество банков памяти | 32 банка (группы по 8 банков) 8 Гбит x 4 банка (16–64 Гбит x4/x8) 8 Гбит x 2 банка (8 Гбит x4/x8) 16 банков (группы по 4 банка) 4 Гбит x 4 банка (16–64 Гбит x16) 4 Гбит x 2 банка (8 Гбит x16) |

| Размер пакета (x4 / x8 / x16) | 1 КБ / 1 КБ / 2 КБ |

| Предварительная выборка | 16n |

| DCA (регулировка цикла нагрузки) | DQS и DQ |

| Внутренний мониторинг задержки DQS | Генератор интервалов DQS |

| ODECC (On-die ECC) | Обнаружение и исправление ошибок 128b+8b SEC |

| CRC (циклическая проверка с избыточностью) | Чтение/запись |

| ODT (On-die Termination) | Шина DQ, DQS, DM, CA |

| MIR ("зеркальный" контакт) | Да |

| Инверсия шины | Инверсия команды/адреса (CAI) |

| CA обучение, CS обучение | CA обучение, CS обучение |

| Выравнивание записи и Режимы обучения | Улучшенный |

| Шаблоны обучения Чтение | Выделенные MR для заданных пользователем шаблонов обучения последовательных операций и тактовой частоты и сгенерированных LFSR шаблонов |

| Регистры режима работы | До 256 x 8 бит |

| Команды PRECHARGE | Все банки, отдельные банки и тот же банк памяти |

| Команды REFRESH | Все банки и тот же банк памяти |

| Петлевой режим | Да |