Zatwierdzona przez wiodących na świecie producentów płyt głównych{{Footnote.N64682}}

Przetestowana i zatwierdzona pamięć pozwoli Ci bez obaw budować i modernizować swoją konfigurację na preferowanej płycie głównej.

DDR5 to piąta generacja synchronicznej pamięci dynamicznej o dostępie swobodnym i podwójnej szybkości transmisji danych – inaczej SDRAM DDR5. Wszystko zaczęło się w 2017 r., gdy branżowa organizacja standaryzacyjna JEDEC (Joint Electron Device Engineering Council) z udziałem wiodących na świecie świecie dostawców architektury półprzewodników i układów pamięci, w tym firmy Kingston, określiła standard pamięci DDR5 wraz z nowymi rozwiązaniami, które zapewniają wyższą wydajność, niższy pobór energii i bardziej trwałą integralność danych na kolejne lata rozwoju technologii komputerowej. Pamięć DDR5 pojawiła się na rynku w 2021 r.

Minimalna szybkość pamięci DDR5 to 4800MT/s{{Footnote.A65242}}, podczas gdy pamięć DDR4 osiąga maksymalnie 3200MT/s. Oznacza to o 50% większą przepustowość. Zaplanowano, że wraz z wprowadzaniem nowych platform obliczeniowych standardowa szybkość pamięci DDR5 zwiększy się do 8800MT/s, a być może nawet do większej wartości.

Przy napięciu 1,1V pamięć DDR5 zużywa o ok. 20% mniej energii niż analogiczne komponenty DDR4 przy napięciu 1,2V. Pozwala to wydłużyć czas pracy na baterii w laptopach, ale jest także istotną zaletą w przypadku serwerów korporacyjnych pracujących przez całą dobę.

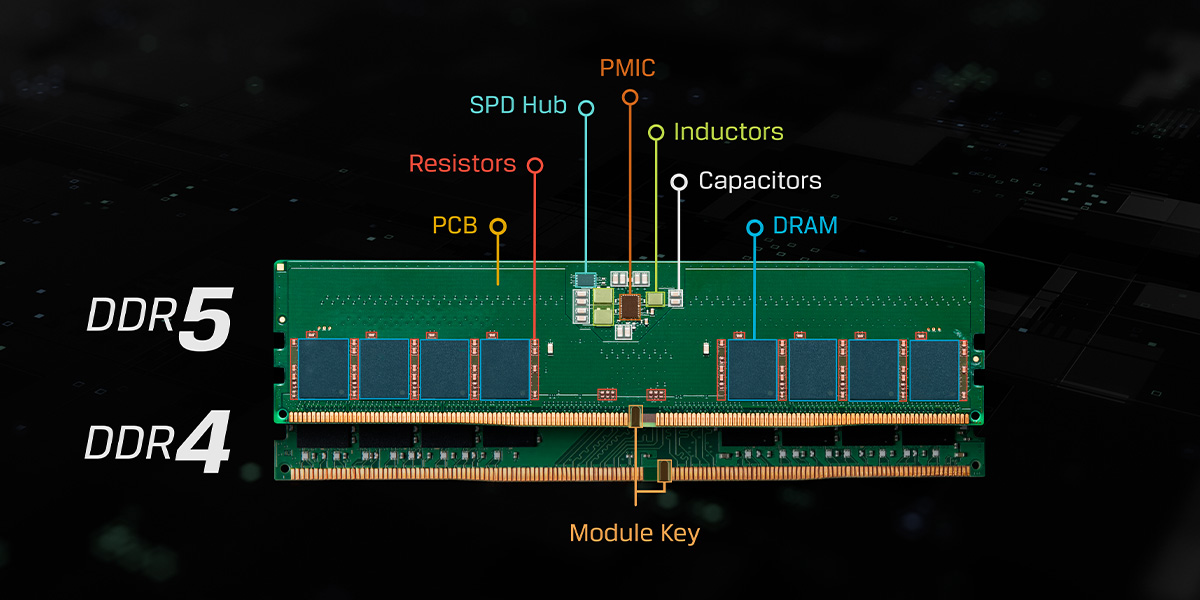

Moduły pamięci DDR5 mają wbudowane układy zarządzania energią (PMIC), które pomagają regulować parametry zasilania różnych komponentów modułu pamięci (DRAM, rejestr, koncentrator SPD itp.). W przypadku modułów klasy serwerowej układ PMIC wykorzystuje napięcie 12V, a w przypadku modułów przeznaczonych do komputerów PC – 5V. Zapewnia to lepszą dystrybucję zasilania niż modułach pamięci wcześniejszych generacji, poprawia integralność sygnałów i ogranicza zakłócenia.

Pamięć DDR5 wykorzystuje nowy układ łączący pamięć EEPROM Serial Presence Detect (SPD) z dodatkowymi funkcjami koncentratora, który zarządza dostępem do zewnętrznego kontrolera i oddziela obciążenie pamięci na magistrali wewnętrznej od magistrali zewnętrznej.

Moduł pamięci DDR5 jest podzielony na dwa niezależne 32-bitowe adresowalne podkanały w celu zwiększenia wydajności i zmniejszenia opóźnień dostępu do danych dla kontrolera pamięci. Szerokość szyny danych modułu DDR5 jest nadal 64-bitowa, jednak podział na dwa 32-bitowe adresowalne kanały zwiększa ogólną wydajność. W przypadku pamięci klasy serwerowej (RDIMM) do każdego podkanału dodawanych jest 8 bitów na potrzeby obsługi funkcji ECC, co daje łącznie 40 bitów na podkanał lub 80 bitów na szereg. Moduły Dual Rank mają cztery podkanały 32-bitowe.

Wycięcie w środku modułu pełni funkcję klucza, który pozwala na dopasowanie do gniazd pamięci DDR5 i jednocześnie zapobiega instalacji pamięci DDR4, DDR3 lub innych nieobsługiwanych typów modułów. W odróżnieniu od pamięci DDR4 klucze modułów DDR5 różnią się w zależności od typu modułów: UDIMM i RDIMM.

Wbudowana funkcja korekcji ECC (Error Correction Code) to nowe rozwiązanie stworzone z myślą o korygowaniu błędów bitowych w module pamięci DRAM. Wraz ze zwiększeniem gęstości układów pamięci DRAM dzięki zagęszczeniu litografii płytek rośnie ryzyko utraty danych. Ogranicza je wbudowana funkcja korekcji ECC, która koryguje błędy w układzie, zwiększa niezawodność i zmniejsza liczbę defektów. Technologia ta nie pozwala na korygowanie błędów poza układem lub błędów występujących na magistrali między modułem a kontrolerem pamięci w procesorze. Procesory obsługujące technologię ECC do serwerów i stacji roboczych są wyposażone w funkcję kodowania, która może na bieżąco korygować błędy jedno- lub wielobitowe. Aby możliwa była tego typu korekcja, niezbędna jest dostępność dodatkowych bitów pamięci DRAM, zapewniana w modułach klasy ECC, takich jak moduły ECC niebuforowane, rejestrowe i o zmniejszonym obciążeniu.

Moduły DDR5 RDIMM klasy serwerowej są wyposażone w dodatkowe czujniki temperatury na końcach modułów, umożliwiające monitorowanie warunków termicznych na całej długości modułu DIMM. Pozwala to na bardziej precyzyjną kontrolę chłodzenia systemu – w odróżnieniu od pamięci DDR4, w przypadku której występuje problem ograniczenia wydajności w wysokich temperaturach.

W pamięci DDR5 podwojono liczbę banków z 16 do 32. Pozwala to na jednoczesne otwarcie większej liczby stron, zwiększając wydajność. Podwojono także minimalną długość pakietu z 8 (pamięć DDR4) do 16. Poprawia to wydajność magistrali danych dzięki zapewnieniu dwukrotnie większej ilości danych, a w konsekwencji pozwala zmniejszyć liczbę odczytów/zapisów w celu uzyskania dostępu do tej samej linii danych w pamięci podręcznej.

W pamięci DDR5 dodano nowe polecenie o nazwie SAME-BANK Refresh, które umożliwia odświeżenie tylko jednego banku w grupie zamiast wszystkich. W porównaniu z pamięcią DDR4 pozwala to na dalszą poprawę wydajności i efektywności.

Pamięć DDR5 wykorzystuje filtr DFE (Decision Feedback Equalization), aby zapewniać stabilną, niezawodną integralność sygnału w module, wymaganą dla dużej przepustowości.

Chociaż same moduły pamięci wyglądają podobnie do modułów DDR4, wprowadzono znaczące zmiany, które sprawiają, że są one niezgodne ze starszymi systemami. Zmieniono umiejscowienie klucza (wycięcie pośrodku), aby uniemożliwić ich instalację w niekompatybilnych gniazdach.

Przetestowana i zatwierdzona pamięć pozwoli Ci bez obaw budować i modernizować swoją konfigurację na preferowanej płycie głównej.

| Szybkość transmisji danych (w MT/s){{Footnote.A65242}} | 3600, 4000, 4400, 4800, 5200, 5600, 6000, 6400, 6800, 7200, 7600, 8000, 8400, 8800 |

| Gęstości monolitycznej pamięci DRAM (Gbit) | 8Gb, 16Gb, 24Gb, 32Gb, 48Gb, 64Gb |

| Typ pakietu i schemat połączeń (x4, x8 / x16) | BGA, 3DS TSV (78, 82 / 102) |

| Interfejs | |

|---|---|

| Napięcie (VDD / VDDQ / VPP) | 1,1 / 1,1 / 1,8 V |

| Wewnętrzne VREF | VREFDQ, VREFCA, VREFCS |

| Polecenie/adres | POD (Pseudo Open Drain) |

| Korekcja | DFE (Dynamic Feedback Equalization) |

| Długość pakietu | BL16 / BC8 / BL32 (opcjonalnie) |

| Architektura podstawowa | |

| Liczba banków | 32 banki (8 grup banków) 8 gr. x 4 banki (16-64Gb x4/x8) 8 gr. x 2 banki (8Gb x4/x8) 16 banków (4 grupy banków) 4 gr. x 4 banki (16-64Gb x16) 4 gr. x 2 banki (8Gb x16) |

| Rozmiar strony (x4 / x8 / x16) | 1KB / 1KB / 2KB |

| Pobieranie wstępne | 16n |

| DCA (Duty Cycle Adjustment) | DQS i DQ |

| Wewnętrzne monitorowanie opóźnienia DQS | Oscylator interwału DQS |

| ODECC (wbudowana funkcja korekcji ECC) | Kontrola i korygowanie błędów SEC 128b+8b |

| CRC (cykliczna kontrola nadmiarowości) | Odczyt/zapis |

| ODT (układy terminujące wewnątrz pamięci) | DQ, DQS, DM, magistrala CA |

| MIR (pin „Mirror”) | Tak |

| Odwrócenie magistrali | Inwersja polecenia/adresu (CAI) |

| CA Training, CS Training | CA training, CS training |

| Tryby uczenia równoważenia zapisu | Ulepszone |

| Wzorce uczenia odczytu | Dedykowane rejestry trybów dla zdefiniowanych przez użytkownika wzorców uczenia – szeregowych, zegarowych i generowanych przez LFSR |

| Rejestry trybów | Do 256 x 8 bitów |

| Polecenia PRECHARGE | Wszystkie banki, jeden bank, ten sam bank |

| Polecenia REFRESH | Wszystkie banki, ten sam bank |

| Tryb pętli zwrotnej | Tak |