Qualifiée par les plus grands fabricants de cartes mères au monde{{Footnote.N64682}}

Testée et approuvée pour que tu puisses construire et mettre à niveau en toute confiance en te reposant sur ta carte mère préférée.

La DDR5 est la cinquième génération de mémoire vive dynamique synchrone à double débit de données, ou DDR5 SDRAM. Amorcée en 2017 par l’organisme de normalisation du secteur JEDEC (Joint Electron Device Engineering Council) avec la contribution des principaux fournisseurs mondiaux de semi-conducteurs de mémoire et d’architecture de chipset, dont Kingston, la DDR5 est conçue avec de nouvelles fonctionnalités pour des performances accrues, une consommation réduite et une intégrité des données plus robuste pour la prochaine décennie informatique. La DDR5 a été lancée en 2021.

La DDR5 démarre à 4 800 MT/s{{Footnote.A65242}}, tandis que la DDR4 plafonne à 3 200 MT/s. Cela représente une augmentation de 50 % de la bande passante. Pour s’aligner sur l’évolution des plateformes de calcul, la DDR5 prévoit des vitesses standard qui s’échelonneront jusqu’à 8 800 MT/s, voire au-delà.

À 1,1 V, la DDR5 consomme environ 20 % moins d’énergie que les composants équivalents de la DDR4 à 1,2 V. Tout en préservant l’autonomie de la batterie des ordinateurs portables, elle présente un avantage considérable pour les serveurs d’entreprise fonctionnant 24 h/24.

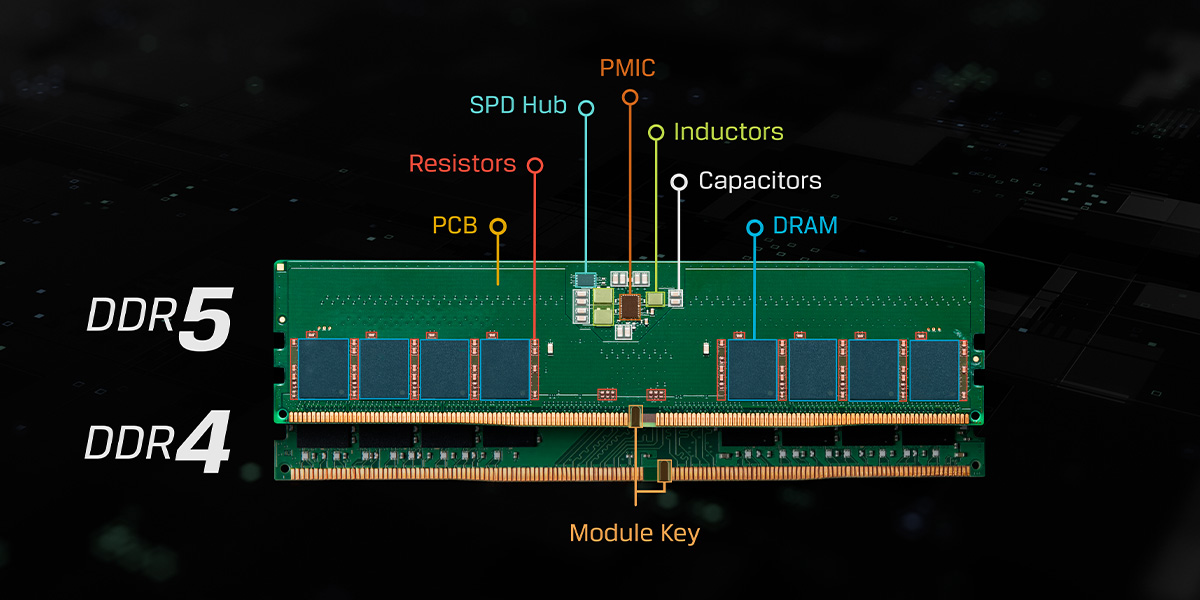

Les modules DDR5 sont dotés de circuits intégrés de gestion de l’énergie (PMIC) intégrés, qui permettent de réguler la puissance requise par les différents composants du module de mémoire (DRAM, registre, hub SPD, etc.). Pour les modules de classe serveur, le PMIC utilise 12 V, et pour les modules de classe PC, le PMIC utilise 5 V. Cela permet une meilleure distribution de l’alimentation par rapport aux générations précédentes, améliore l’intégrité du signal et réduit le bruit.

La DDR5 utilise un nouveau dispositif intégrant l’EEPROM Serial Presence Detect (SPD) avec des fonctions de hub supplémentaires, gérant l’accès au contrôleur externe et découplant la charge mémoire sur le bus interne depuis l’externe.

La DDR5 divise le module de mémoire en deux sous-canaux indépendants adressables sur 32 bits afin d’accroître l’efficacité et de réduire les latences des accès aux données pour le contrôleur de mémoire. La largeur de données du module DDR5 est toujours de 64 bits, mais sa décomposition en deux canaux adressables de 32 bits augmente les performances globales. Pour les mémoires de classe serveur (RDIMM), 8 bits sont ajoutés à chaque sous-canal pour le support ECC, soit un total de 40 bits par sous-canal, ou 80 bits par rang. Les modules Dual Rank disposent de quatre sous-canaux de 32 bits.

L’encoche au centre du module agit comme une clé, s’alignant sur les sockets DDR5 pour empêcher l’installation de modules DDR4, DDR3 ou d’autres types de modules non pris en charge. Contrairement à la DDR4, les clés des modules DDR5 diffèrent selon les types de modules : UDIMM et RDIMM

Le code de correction d’erreur (ECC) sur puce est une nouvelle fonctionnalité conçue pour corriger les erreurs de bits dans la puce DRAM. À mesure que la densité des puces DRAM augmente grâce à la lithographie des plaquettes rétrécies, le risque de fuite de données augmente. L’ECC sur puce atténue ce risque en corrigeant les erreurs à l’intérieur de la puce, ce qui augmente la fiabilité et réduit les taux de défaillances. Cette technologie ne peut pas corriger les erreurs extérieures à la puce ou celles qui se produisent sur le bus entre le module et le contrôleur de mémoire logé dans le CPU. Les processeurs pour serveurs et stations de travail dotés de la technologie ECC présentent un codage capable de corriger à la volée des erreurs d’un ou plusieurs bits. Des bits supplémentaires de DRAM doivent être disponibles pour permettre cette correction, ce qui est le cas des modules de classe ECC tels que ECC sans tampon, enregistré et

Les modules DDR5 RDIMM de classe serveur sont équipés de capteurs de température aux extrémités des modules afin de surveiller les conditions thermiques sur toute la longueur du module DIMM. Cela permet un contrôle plus précis du refroidissement du système, par opposition à l’étranglement des performances observé dans la DDR4 avec les températures élevées.

La DDR5 double les banques de 16 à 32. Cela permet d’ouvrir plus de pages à la fois, ce qui augmente l’efficacité. La longueur minimale des rafales est également doublée, passant de 8 à 16 pour la DDR4. Cela améliore l’efficacité du bus de données, en fournissant deux fois plus de données sur le bus, et réduit par conséquent le nombre de lectures/écritures pour accéder à la même ligne de données du cache.

La DDR5 ajoute une nouvelle commande appelée SAME-BANK Refresh, qui permet de rafraîchir une seule banque par groupe de banques, plutôt que toutes les banques. Par rapport à la DDR4, cette commande permet à la DDR5 d’améliorer encore davantage ses performances et son efficacité.

La DDR5 utilise l’égalisation dynamique à rétroaction (DFE) pour fournir une intégrité de signal stable et fiable sur le module, nécessaire pour une large bande passante.

Si les modules de mémoire eux-mêmes semblent similaires à la DDR4, ils présentent des modifications importantes qui les rendent incompatibles avec les systèmes existants. L’emplacement de la clé (encoche au centre) se déplace pour éviter qu’ils ne soient installés dans des sockets incompatibles.

Testée et approuvée pour que tu puisses construire et mettre à niveau en toute confiance en te reposant sur ta carte mère préférée.

| Débits de données (vitesse en MT/s){{Footnote.A65242}} | 3 600, 4 000, 4 400, 4 800, 5 200, 5 600, 6 000, 6 400, 6 800, 7 200, 7 600, 8 000, 8 400, 8 800 |

| Densités de DRAM monolithique (Gbit) | 8 Go, 16 Go, 24 Go, 32 Go, 48 Go, 64 Go |

| Type de boîtier et Ballout (x4, x8 / x16) | BGA, 3DS TSV (78, 82 / 102) |

| Interface | |

|---|---|

| Tension (VDD / VDDQ / VPP) | 1,1 / 1,1 / 1,8 V |

| VREF interne | VREFDQ, VREFCA, VREFCS |

| Commande/Adresse | POD (Pseudo Open Drain) |

| Égalisation | DFE (égalisation dynamique à rétroaction) |

| Longueur de rafale | BL16 / BC8 / BL32 (en option) |

| Architecture centrale | |

| Nombre de banques | 32 banques (8 groupes de banques) 8 BG x 4 banques (16-64 Go x4/x8) 8 BG x 2 banques (8 Go x4/x8) 16 banques (4 groupes de banques) 4 BG x 4 banques (16-64Gb x16) 4 BG x 2 banques (8 Go x16) |

| Taille de page (x4 / x8 / x16) | 1 Ko / 1 Ko / 2 Ko |

| Préfixe | 16n |

| DCA (ajustement du cycle de travail) | DQS et DQ |

| Surveillance interne du délai DQS | Oscillateur d’intervalle DQS |

| ODECC (ECC sur puce) | Contrôle d’erreur et scrub SEC 128b+8b |

| CRC (contrôle de redondance cyclique) | Lecture/écriture |

| ODT (terminaison sur puce) | Bus DQ, DQS, DM, CA |

| MIR (broche « miroir ») | Oui |

| Inversion de bus | Inversion commande/adresse (CAI) |

| Formation CA, formation CS | Formation CA, formation CS |

| Modes de formation à l’égalisation de l’écriture | Améliorée |

| Modèles de formation à la lecture | MR dédiés pour les motifs d’apprentissage générés par l’utilisateur (série, horloge, LFSR) |

| Registres de mode | Jusqu’à 256 x 8 bits |

| Commandes PRECHARGE | Toutes les banques, par banque, et même banque |

| Commandes REFRESH | Toutes les banques et la même banque |

| Mode Loopback | Oui |