ECC และ Spare Blocks ช่วยปกป้องข้อมูลใน SSD Kingston ไม่ให้เกิดความผิดพลาด

ระบบป้องกันข้อมูลจากต้นทางถึงปลายทาง

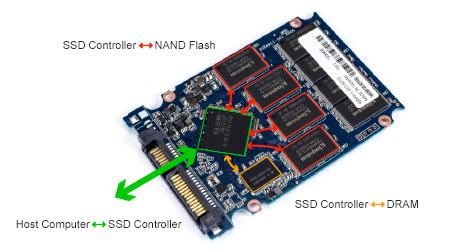

Kingston SSD ทั้งหมดมีระบบป้องกันข้อมูลจากต้นทางถึงปลายทางที่ช่วยปกป้องข้อมูลของลูกค้าทันทีที่ถูกโอนโดยเครื่องโฮสต์ไปยัง SSD และจาก SSD ไปยังคอมพิวเตอร์โฮสต์